← Back to Projects

HAShCache: Heterogeneity Aware Shared DRAMCache for Integrated Heterogeneous Systems (IHS)

► Appears in ACM Transactions on Architecture & Code Optimization - TACO 2017

► Presented at HiPEAC 2018, Manchester, UK

► IISc EECS 2017 Best Poster Award

► Source code available on Github

What is HAShCache?

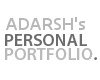

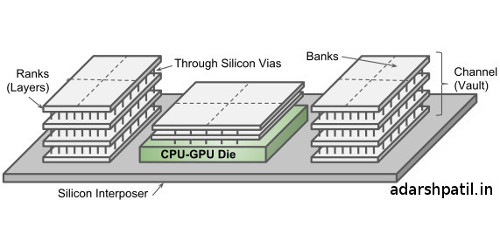

It is a shared last-level die-stacked DRAM cache for a integrated heterogeneous CPU-GPU processor. HAShCache is heterogeneity-aware and can adapt dynamically to address the inherent disparity of demands in such an architecture. It combines an intelligent DRAM request scheduler (PrIS), a selective temporal bypass scheme (ByE) and an cache-line occupancy controlling mechanism (Chaining).

Features and Properties (a) Provides low average memory access latency for CPU requests

(b) Ability to utilize aggregate bandwidth of stacked DRAM and off-chip DRAM

(c) Intelligent DRAM request Scheduling: prioritization scheme for scheduling CPU requests at the DRAMCache controller;

(d) selective and temporal bypassing scheme for CPU requests

(e) working set aware occupancy controlling mechanism for GPU lines in the DRAMCache through pseudo-associativity