### Improving Reliability and Performance of Datacenter Systems via Coherence

Adarsh Patil

3<sup>rd</sup> Year PhD student

## Outline

Improving Reliability and Performance

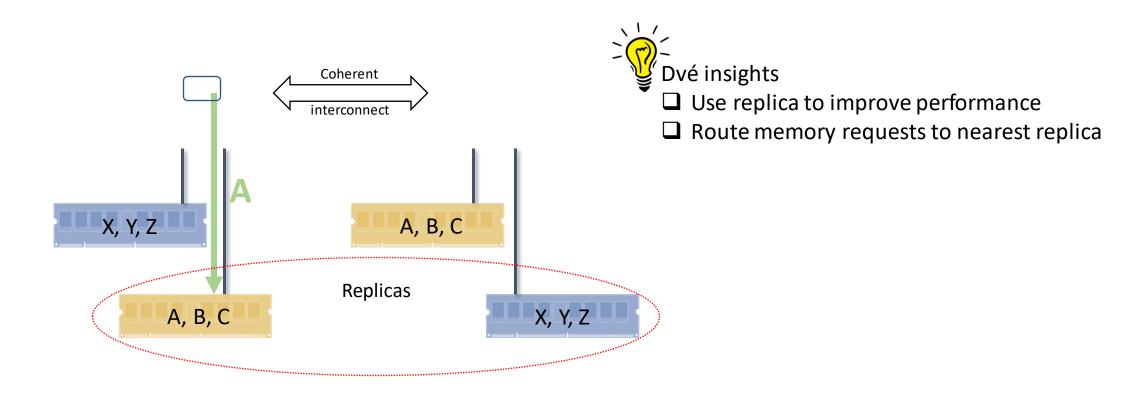

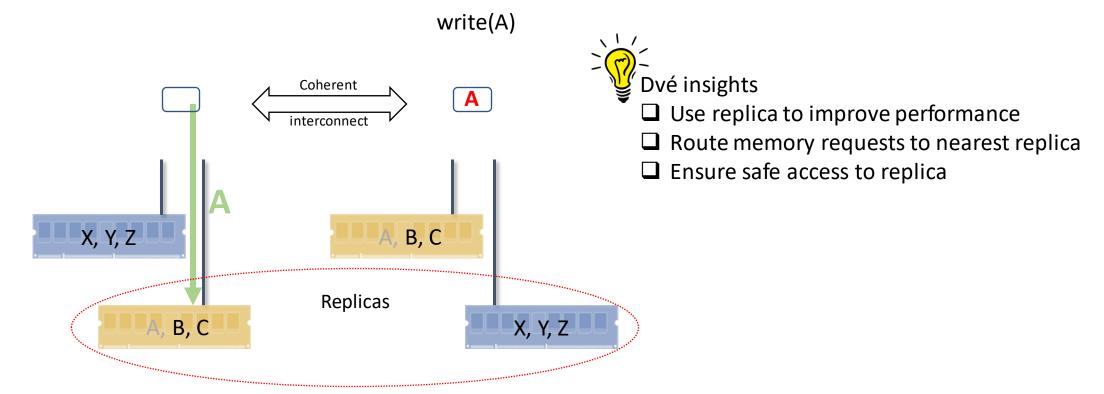

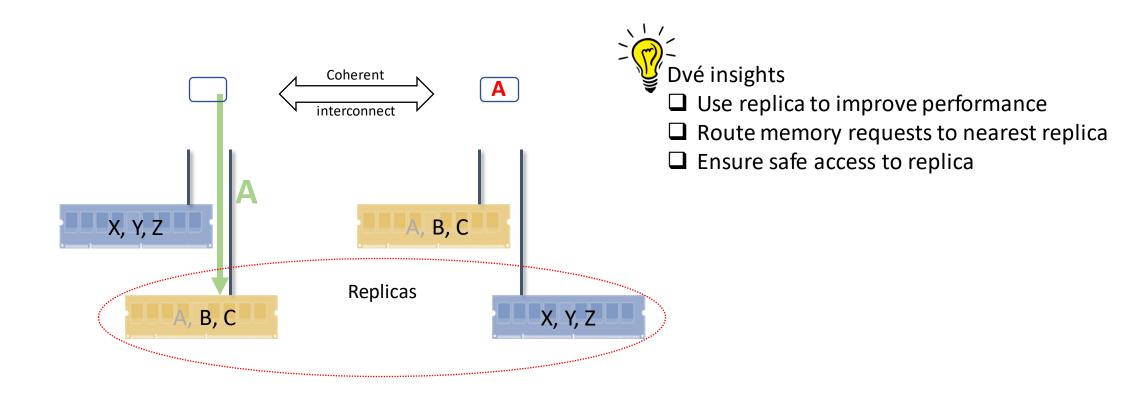

Dvé: Coherent Replication for DRAMs (ISCA 2021)

Coherent Disaggregated Shared Memory for FaaS (WIP)

## Outline

Improving Reliability and Performance

#### Dvé: Coherent Replication for DRAMs (ISCA 2021)

Coherent Disaggregated Shared Memory for FaaS (WIP)

### Dvé: Outline

Performance gains

**On-demand Reliability**

## Outline

On-demand Reliability

# Increasing DRAM Faults

Bloomberg

#### Markets

#### How One Piece of Hardware Took Down a \$6 Trillion Stock Market

By <u>Gearoid Reidy, Shoko Oda, Min Jeong Lee</u>, and <u>Toshiro Hasegawa</u> 2 October 2020, 10:47 BST *Updated on 5 October 2020, 01:48 BST*

That all changed on Thursday, when a piece of hardware called the No. 1 shared disk device, one of two square-shaped data-storage boxes, detected a memory error. These devices store management data used across the servers, and distribute information such as commands and ID and password combinations for terminals that monitor trades.

#### RAMBleed Reading Bits in Memory Without Accessing Them

RAMBleed is a side-channel attack that enables an attacker to read out physical memory belonging to other processes. The implications of violating

#### ECCPLOIT: ECC MEMORY VULNERABLE TO ROWHAMMER ATTACKS AFTER ALL

Where many people thought that high-end servers were safe from the (unpatchable) <u>Rowhammer</u> bitflip

#### Google: DRAM error rates vastly higher than previously thought

PCs will likely require error correction code in the future due to DRAM issues

() 🖸 🗇 🜍 🕞

#### By Lucas Mearian

Senior Reporter, Computerworld | 8 OCTOBER 2009 23:51 GMT

#### Wet Q MENU L. U

#### DRAM error rates: Nightmare on DIMM street

A two-and-a-half year study of DRAM on 10s of thousands Google servers found DIMM error rates are hundreds to thousands of times higher than thought -- a mean of 3,751 correctable errors per DIMM per year.This is the world's first large-scale study of RAM errors in the field.

#### 🔍 in 🖬 f У 🖬 🐥

#### Wet Q MENU L• UK

#### DRAM errors: from soft to hard

Every system uses dynamic random access memory (DRAM), but how good is it? Bad news: not nearly as good as vendors would like us to think. Good news: we're learning.

#### 🔍 in 🖬 f У 🖴 🔺

By Robin Harris for Storage Bits | October 24, 2012 -16:26 GMT (17:26 BST) | Topic: Storage

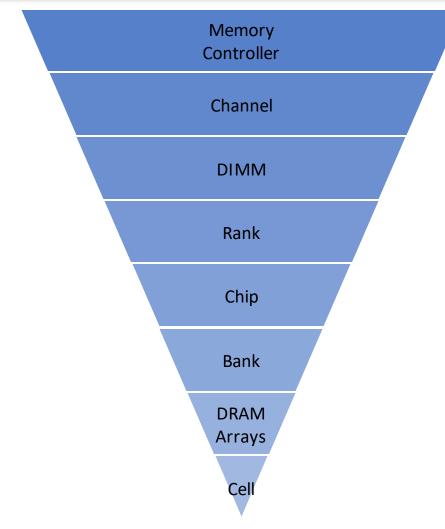

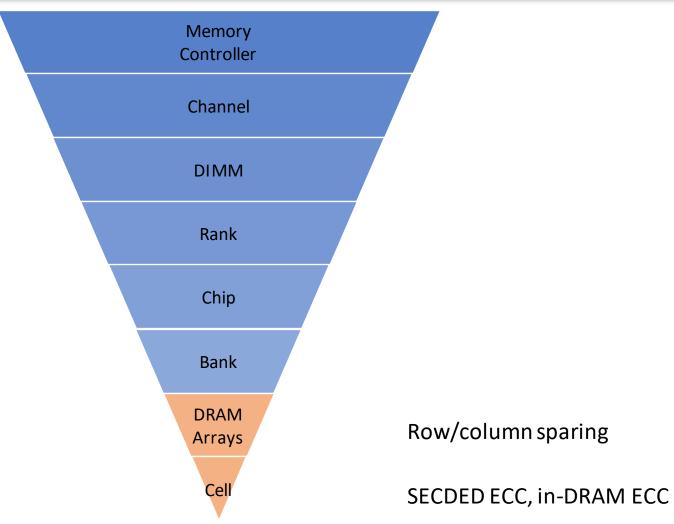

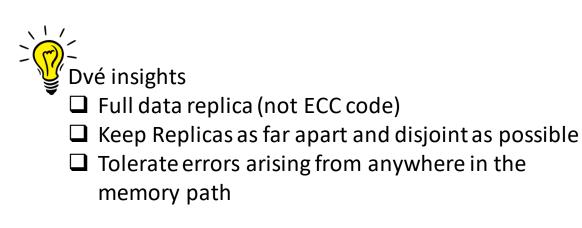

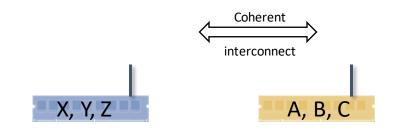

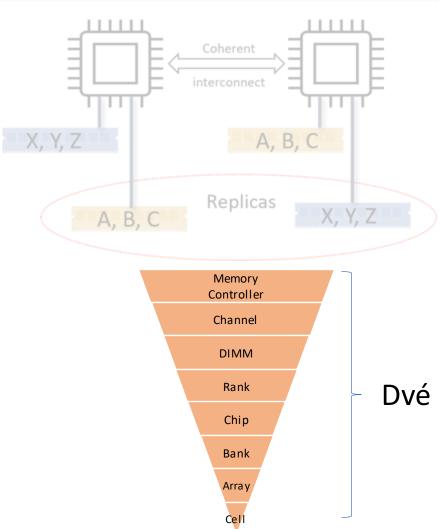

#### Dvé insights

- □ Full data replica (not ECC code)

- □ Keep Replicas as far apart and disjoint as possible

- Tolerate errors arising from anywhere in the memory path

#### For Detection

- **Existing ECC**, CRC, Parity

- □ Strong detection-only code

- Other diagnostic capabilities

#### For Correction

Rely on replica

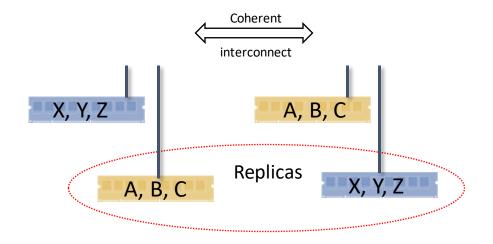

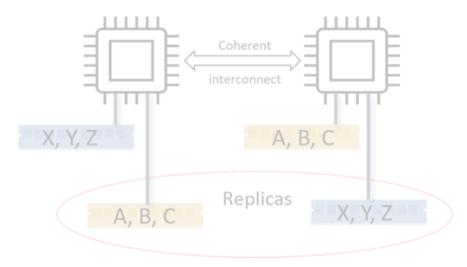

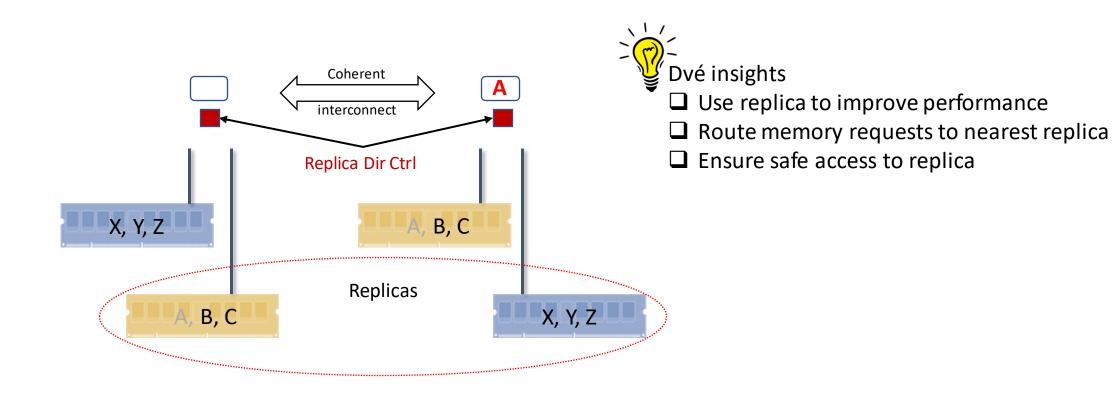

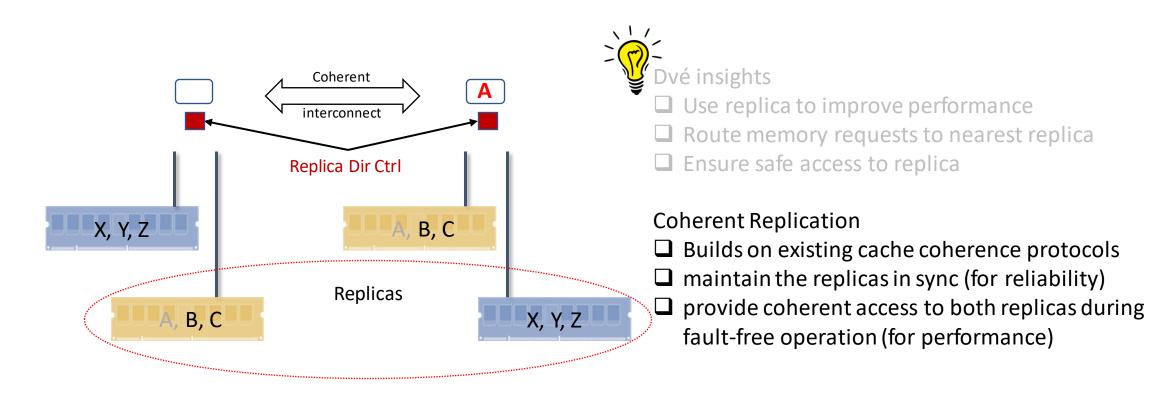

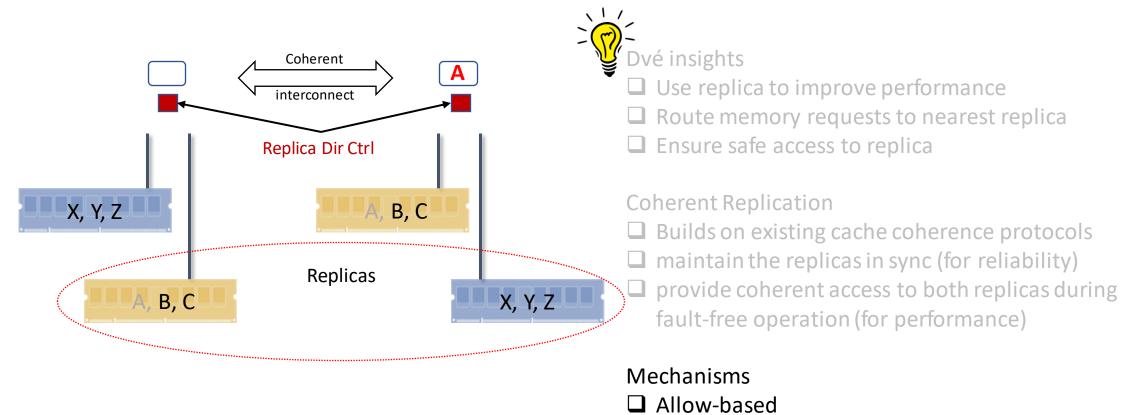

#### Dvé insights

- □ Full data replica (not ECC code)

- □ Keep Replicas as far apart and disjoint as possible

- Tolerate errors arising from anywhere in the memory path

For Detection

- **Existing ECC**, CRC, Parity

- □ Strong detection-only code

- Other diagnostic capabilities

For Correction Rely on replica

# Outline

**On-demand Reliability**

Deny-based

# Outline

**On-demand Reliability**

Skewed memory utilization

□ 50% of the memory is idle in 90% of the servers

□ Provisioning for peak

Utilize idle memory

Overheads applicable only as and when demanded by the application

Skewed memory utilization **50%** of the memory is idle 90% of the servers □ Provisioning for peak

Interface to allocate high-reliability memory □ Hardware-software co-design □ OS support

#### )vé insights

- Utilize idle memory

- Overheads applicable only as and when demanded by the application

Skewed memory utilization

50% of the memory is idle 90% of the time

Provisioning for peak

Interface to allocate high-reliability memory

Hardware-software co-design

OS support

#### Flexible trade-off between capacity and reliability

# Summary

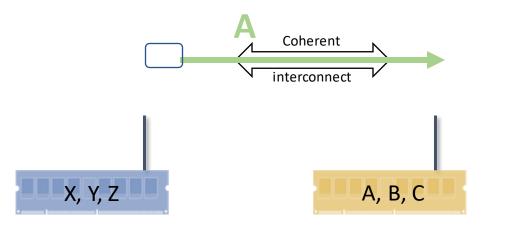

Replication for Reliability

Lowers DUE by

4x over Chipkill 172x over IBM RAIM 11% over Intel Memory Mirroring

**On-demand Replication**

hardware-software co-design using OS/compiler support Coherent Replication for Performance

Improves performance by

5% - 117% over baseline NUMA3% - 107% over an improvedIntel mirroring scheme

Paper in ISCA '21 Artifacts available

https://github.com/adarshpatil/dve https://adar.sh/dve

## Outline

#### Improving Reliability and Performance

#### Dvé: Coherent Replication for DRAMs (ISCA 2021)

#### Coherent Disaggregated Shared Memory for FaaS (WIP)

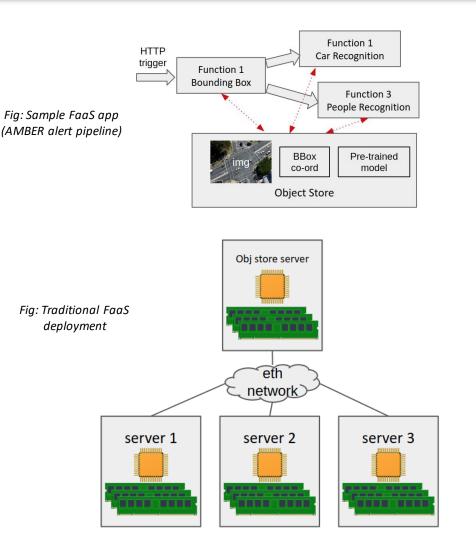

## Function-as-a-Service characteristics

#### **FaaS Applications**

- Composition of stand-alone functions

- DAG invocation sequence

#### **FaaS Functions**

- Stateless: No access to state created by previous invocations

- object store backend with a get/put API

#### FaaS execution Infrastructure

- managed by cloud provider

- Scales by adding/removing function instances

- Runtime orchestrates and load balances

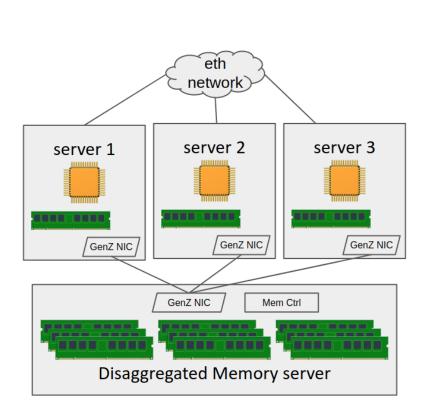

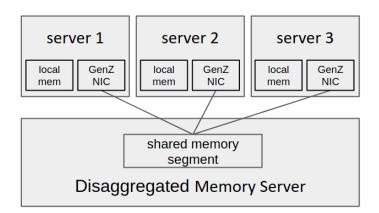

#### Our proposal: FaaS-DM

Fig: FaaS with Disaggregated Shared Memory

FaaS with Disaggregated Shared Memory

- ✓ Hardware caching

- Benefit from hardware prefetching and intranode coherence

- ✓ Application transparent caching

- Implicit data movement using inter-node hardware cache coherence

- Use existing shared memory synchronization techniques

- ✓ Avoids overfetch and critical path writeback

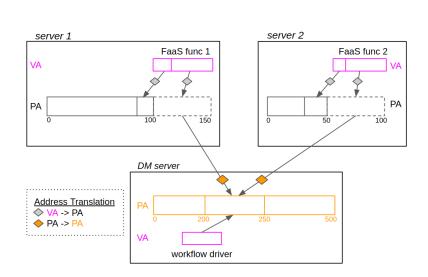

## Open Problems in FaaS-DM

Fig: FaaS-DM logical view

#### Address mapping and translation

- Sharing the same physical memory region between independent servers

- Communication/co-ordination between executing functions

#### Performance

• Optimizing inter-node coherence protocol

#### Availability

• Partial system failure (non-fate sharing)

# Our approach

Fig: FaaS-DM addressing schematic

#### Address mapping and translation

- Extends shared memory inter-process communication (IPC) [POSIX API: shm\_open, shm\_close, mmap]

- Extends annexation process to allow mapping of FaaS-DM memory segment into FaaS function VA

- OS's exchange messages via RPC for naming and identification of FaaS-DM memory segments [LegoOS, OSDI '18]

- Address translation similar to 2-level page table [DeACT, HPCA '21]

# Our approach

- Sharing characteristics of FaaS workloads

- Imposed function execution limits

- Non-blocking coherence protocol to guarantee forward progress

- Atomic durability and Memory consistency guarantees

# Summary

#### Improving Reliability and Performance

#### Dvé: Coherent Replication for DRAMs (ISCA 2021)

#### Coherent Disaggregated Shared Memory for FaaS (WIP)